# CMT2189B User Guide

# **Overview**

The CMT2189B is a low power, high performance, Flash-based, OOK RF transmitter chip embedded with the RISK MCU, which covers a wireless communication band of 240 - 960 MHz. The product is a part of the CMOSTEK NextGenRF<sup>™</sup> product family which covers a complete product line consisting of transmitters, receivers, transceiver, etc.

The product models covered in this document are shown in the table below.

| Product<br>Model | Frequency<br>Range | Modulation<br>Method | Tx Power | Tx Current | Configuration   | Package |

|------------------|--------------------|----------------------|----------|------------|-----------------|---------|

| CMT2189B         | 240 - 960MHz       | ООК                  | +13 dBm  | 17.5 mA    | Embedded<br>MCU | SOP14   |

## Table 1. Product Models Covered in This Document

#### Notes:

The test condition for the Tx power and Tx current is: 433.92 MHz, CW mode (always in the Tx carrier mode), Tx mode of Duty 50% and Tx current of 8.5 mA.

## **Table of Contents**

| 1 | Chip Ar  | chitecture                                      | 5    |

|---|----------|-------------------------------------------------|------|

|   | 1.1 Ove  | rall Operating Principle                        | 5    |

|   | 1.2 IO F | in Description                                  | 5    |

| 2 | RF Part  | Configuration and Control Mechanism             | 8    |

|   |          | rating Mode                                     |      |

|   |          | ple Operating Mode                              |      |

|   |          |                                                 |      |

|   |          | anced Configuration Mode                        |      |

|   |          | Interface Timing                                |      |

|   |          | Configuration Parameter                         |      |

|   |          | figuration Register                             |      |

|   |          | ket Related Register                            |      |

|   | 2.7.1    | Tx Rate                                         |      |

|   | 2.7.2    | Hardware Packet Format                          |      |

|   | 2.7.3    | Preamble                                        |      |

|   | 2.7.4    | Head/Sync                                       |      |

|   | 2.7.5    | Addr/ID                                         |      |

|   | 2.7.6    | Key Value                                       |      |

|   | 2.7.7    | LBD Status Configuration                        |      |

|   | 2.7.8    | Stop Bit Configuration                          |      |

|   | 2.7.9    | Pause/Interval Configuration                    |      |

|   |          | Tcycle Configuration                            |      |

|   |          | e and Function Register                         |      |

|   | 2.8.1    | Soft Reset                                      |      |

|   | 2.8.2    | Operating State and State Switching             |      |

|   | 2.8.3    | Operating State Query                           |      |

|   |          | dware Packet Tx Mode                            |      |

|   | 2.9.1    | Power-up Initialization                         |      |

|   | 2.9.2    | Tx Process                                      |      |

|   |          | s-through Tx Mode (Advanced Configuration Mode) |      |

|   |          | Power-up initialization                         |      |

|   |          | Tx Process                                      |      |

|   | 2.10.3   | Related Register                                | . 31 |

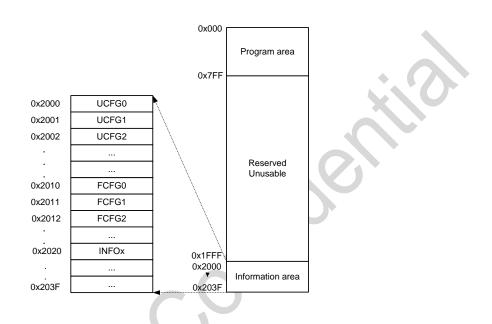

| 3 | Program  | n Memory                                        | 33   |

| 4 | Special  | Function Register(SFR)                          | 34   |

|   | 4.1 Add  | ress Mapping                                    | . 34 |

|   | 4.1.1    | Bank0 SFR                                       | . 34 |

|   | 4.1.2    | BANK1 SFR                                       | . 35 |

|   | 4.1.3    | TMR0 (Addr:0x01)                                | . 36 |

|   | 4.1.4    | STATUS (Addr:0x03)                              | . 36 |

|   | 4.1.5    | PORTA (Addr:0x05)                               | . 38 |

|   | 4.1.6    | PORTC (Addr:0x07)                               | . 38 |

|   | 4.1.7    | INTCON (Addr:0x0B)                              | . 39 |

|   | 4.1.8    | PIR1 (Addr:0x0C)                                | . 40 |

|   | 4.1.9    | TMR2 (Addr:0x11)                                | . 41 |

|   | 4.1.10   | T2CON (Addr:0x12)                               | . 41 |

|    | 4.1.11    | WDTCON (Addr:0x18)                              | 42 |

|----|-----------|-------------------------------------------------|----|

|    | 4.1.12    | CMCON0 (Addr:0x19)                              | 42 |

|    | 4.1.13    | PR0 (Addr:0x1A)                                 | 43 |

|    | 4.1.14    | MSCKCON (Addr:0x1B)                             | 44 |

|    | 4.1.15    | SOSCPR (Addr:0x1C/0x1D)                         | 44 |

|    | 4.1.16    | OPTION (Addr:0x81)                              | 45 |

|    | 4.1.17    | TRISA (Addr:0x85)                               | 46 |

| Та | ble 4-32. | TRISA Bit Function Description                  | 46 |

|    | 4.1.18    | TRISC (Addr:0x87)                               | 46 |

|    |           | PIE1 (Addr:0x8C)                                |    |

|    |           | PCON (Addr:0x8E)                                |    |

|    |           | OSCCON (Addr:0x8F)                              |    |

|    |           | PR2 (Addr:0x92)                                 |    |

|    |           | WPUA (Addr:0x95)                                |    |

|    |           | IOCA (Addr:0x96)                                |    |

|    |           | VRCON (Addr:0x99)                               |    |

|    |           | EEDAT (Addr:0x9A)                               |    |

|    |           | EEADR (Addr:0x9B)                               |    |

|    |           | EECON1 (Addr:0x9C)                              |    |

|    |           | EECON2 (Addr:0x9D)                              |    |

|    |           | Configuration Register UCFGx                    |    |

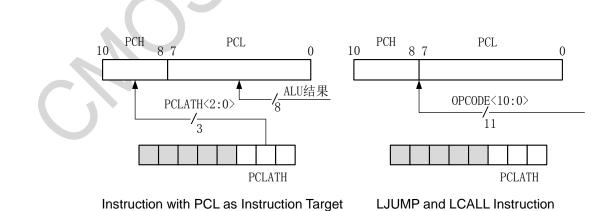

|    |           | PCL and PCLATH                                  |    |

|    |           | INDF and FSR Register                           |    |

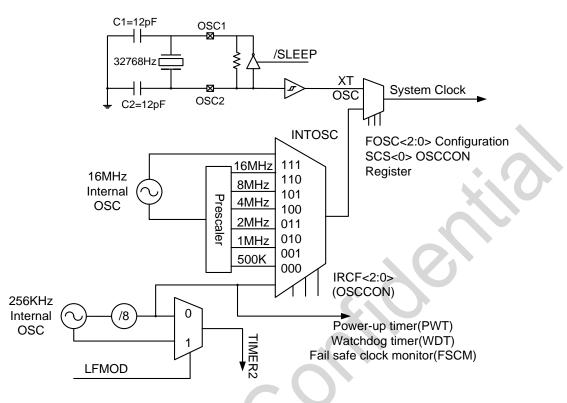

| 5  |           | Clock Source                                    |    |

| J  |           |                                                 |    |

|    | 5.1 Cloc  | k Source Mode                                   | 56 |

|    | 5.2 Exte  | rnal Clock Mode                                 |    |

|    | 5.2.1     | EC Mode                                         | 57 |

|    | 5.2.2     | LP and XT Modes                                 | 57 |

|    | 5.3 Inter | nal Clock Mode                                  | 57 |

|    | 5.3.1     | Frequency Selection Bit (IRCF)                  | 57 |

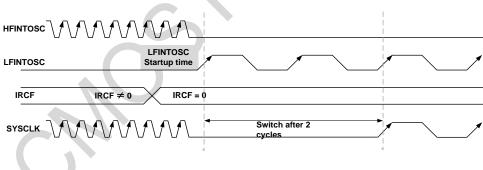

|    | 5.3.2     | Clock Switching Timing of HFINTOSC and LFINTOSC | 58 |

|    | 5.4 Cloc  | k Switching                                     | 58 |

|    | 5.4.1     | System Clock Selection bit (SCS)                | 59 |

|    | 5.4.2     | Oscillator Start-up Timeout State (OSTS) Bit    | 59 |

|    | 5.5 Two   | -Speed Clock Start-up Mode                      | 59 |

|    | 5.5.1     | Two-Speed Start-up Mode Configuration           |    |

|    | 5.5.2     | Two-Speed Start-up Sequence                     |    |

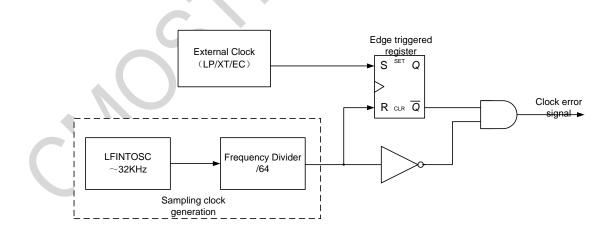

|    | 5.6 Fail- | Safe Clock Monitor                              |    |

|    | 5.6.1     | Fail-Safe Detection                             |    |

|    | 5.6.2     | Fail-Safe Operation                             |    |

|    | 5.6.3     | Fail-Safe Condition Clearing                    |    |

|    | 5.6.4     | Reset or Wake-up from Sleep                     |    |

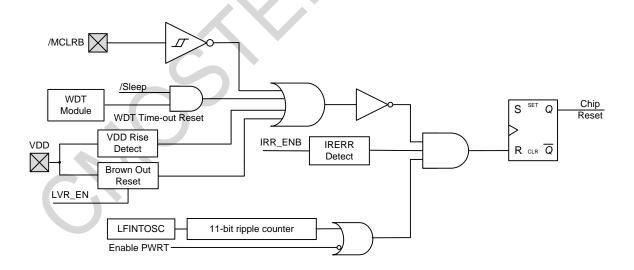

| 6  | Reset T   | iming                                           |    |

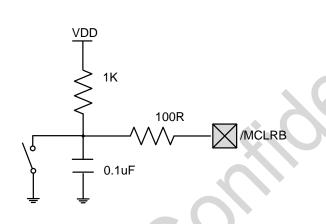

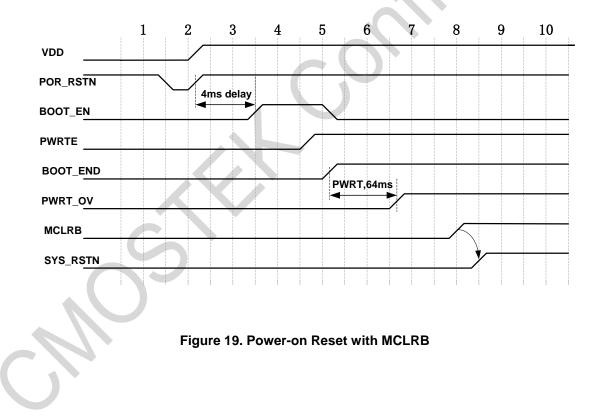

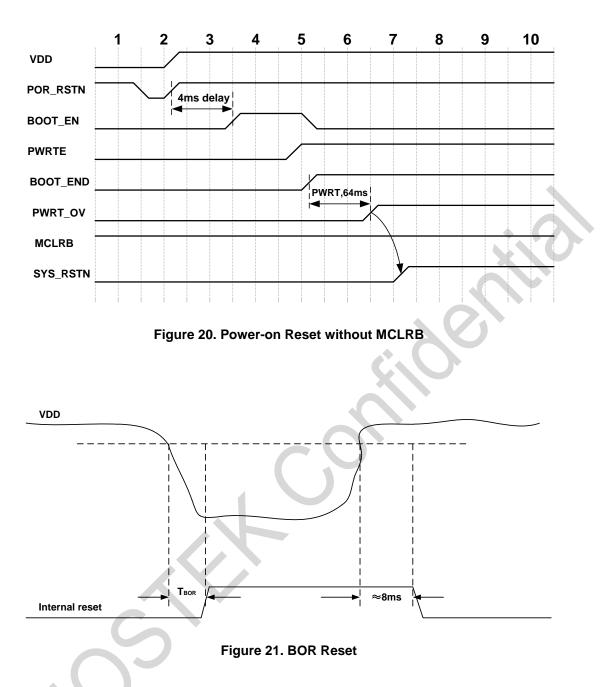

|    | 6.1 Pow   | er-on Reset (POR)                               | 62 |

|    |           | R External Reset (MCLR)                         |    |

|    |           |                                                 |    |

|    |           | er-up Timer (PWRT)                              |    |

|    |           | vn-out Reset / Low Voltage Reset                |    |

|    | 6.5 Erro  | r Instruction Reset                             | 64 |

|    | 6.6 Timeout Action                               | . 64 |

|----|--------------------------------------------------|------|

| 7  | BOOT                                             | 67   |

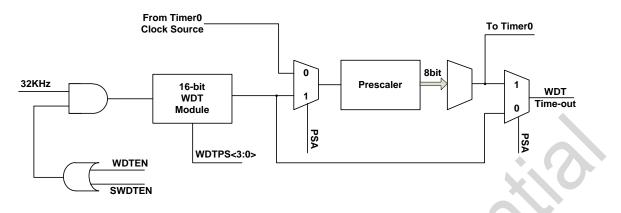

| 8  | Watchdog Timer                                   | 68   |

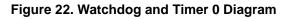

| 9  | Timer 0                                          |      |

|    | 9.1 Timer0 Introduction                          | 60   |

|    | 9.2 Timer Mode of Timer 0                        |      |

|    | 9.3 Counter Mode of Timer 0                      |      |

|    | 9.3.1 Prescaler Circuit Configurable by Software |      |

|    | 9.3.2 Timer 0 Interrupt                          |      |

|    | 9.3.3 Timer 0 Driven by External Clock           |      |

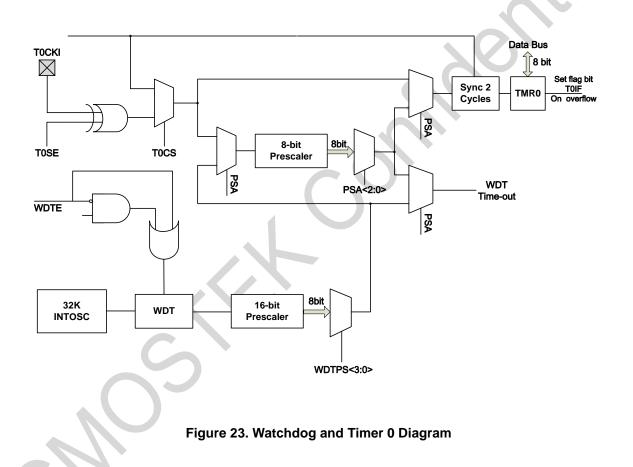

| 10 | Timer 2                                          | 72   |

| 11 |                                                  |      |

| 12 | Data EEPROM                                      |      |

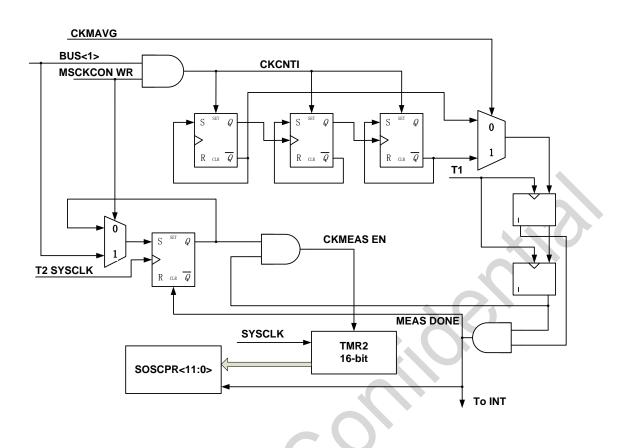

| 12 | Clock Measurement                                |      |

|    |                                                  |      |

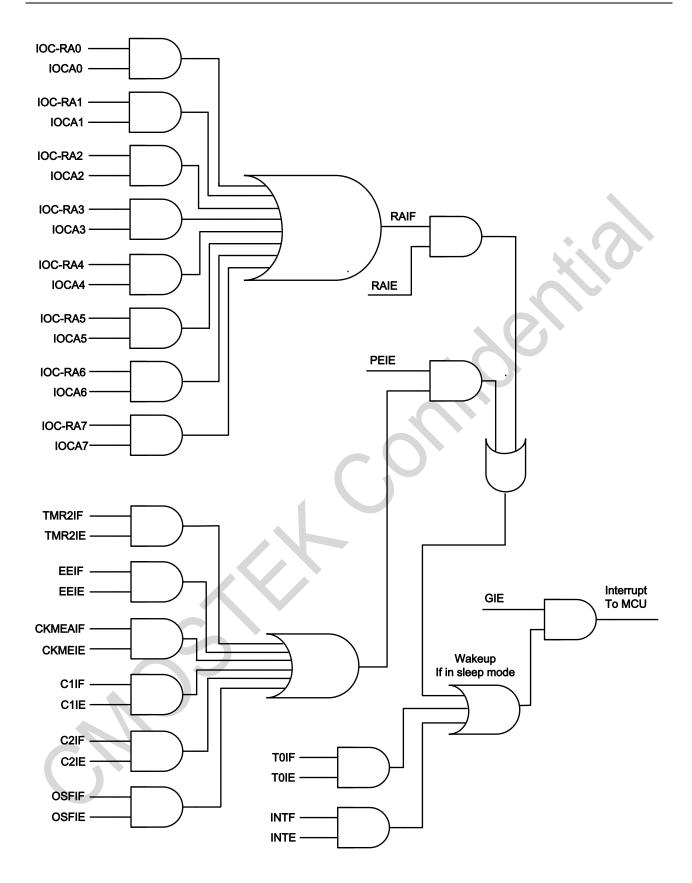

| 14 | Interrupt Mode                                   | 78   |

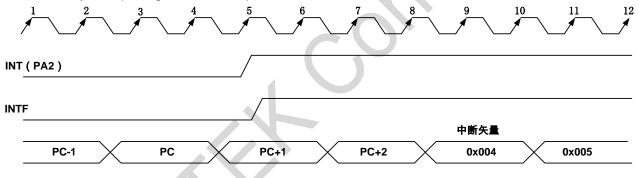

|    | 14.1 INT Interrupt                               | . 78 |

|    | 14.2 PORTA Level Change Interrupt                |      |

|    | 14.3 Interrupt Response                          |      |

|    | 14.4 Context Saving During Interrupts            | . 81 |

| 15 | MCU Sleep Mode for Energy Saving                 |      |

|    | 15.1 Wakeup Mode                                 |      |

|    | 15.2 Watchdog Wake-up                            |      |

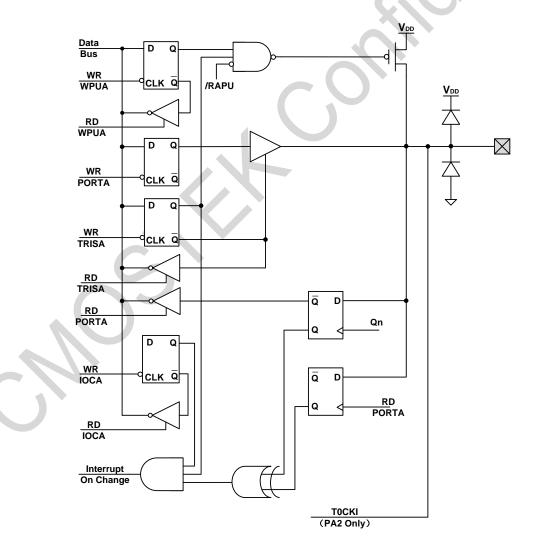

| 16 | I/O Port                                         |      |

|    | 16.1 PORTA Port and TRISA Register               |      |

|    | 16.2 Other Functions of the Port                 |      |

|    | 16.2.1 Weak Pull-Up                              |      |

|    | 16.2.2 Sate Change Interrupt                     |      |

|    | 16.3 Port Description                            |      |

|    | 16.3.1 PORTA<2:0>                                |      |

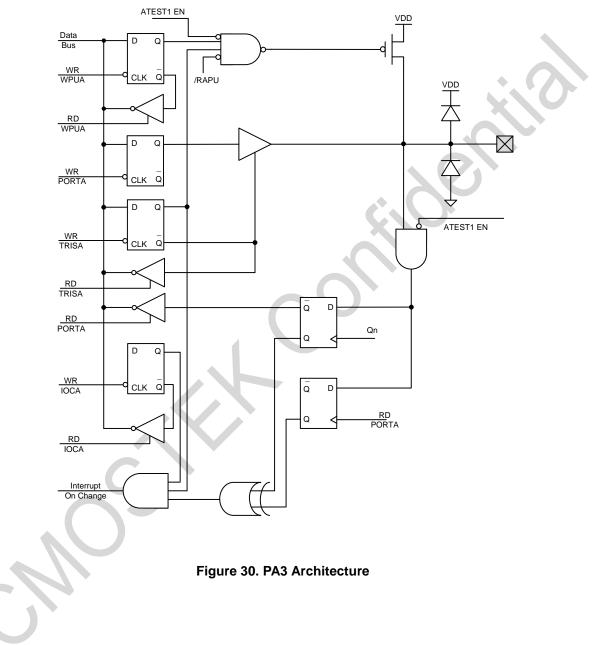

|    | 16.3.2 PORTA3/PA3                                | . 84 |

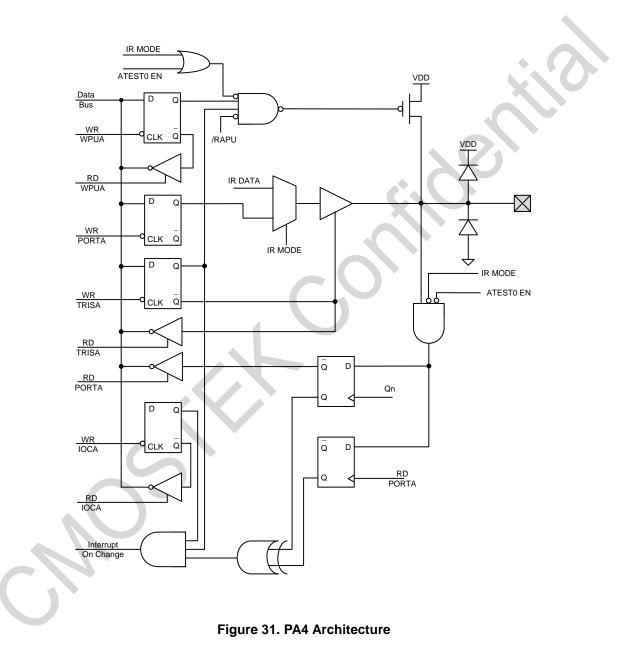

|    | 16.3.3 PORTA4/PA4                                |      |

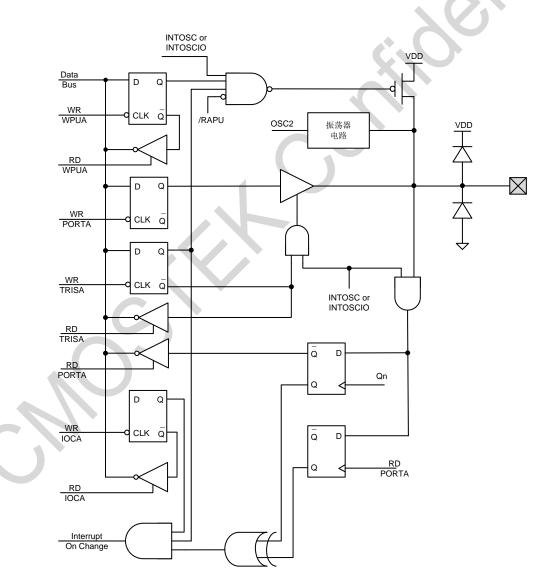

|    | 16.3.4 PORTA5/PA5                                |      |

|    | 16.3.5 PORTA7/PA7                                |      |

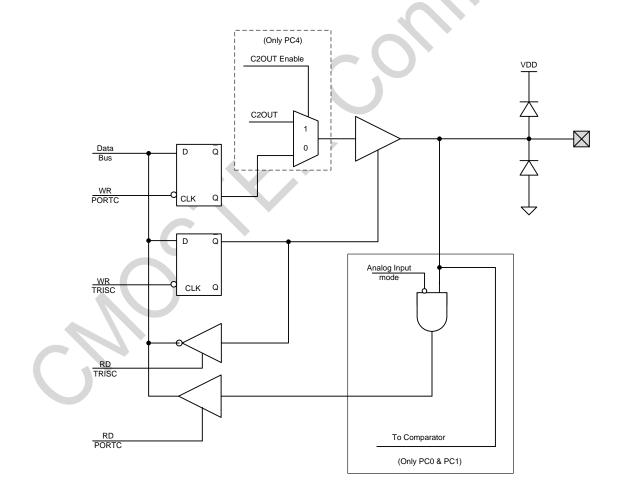

|    | 16.3.6 PORTC<7:0>                                |      |

|    | Instruction Set                                  |      |

| 18 | Revise History                                   | 90   |

| 19 | Contacts                                         | 91   |

# **1 Chip Architecture**

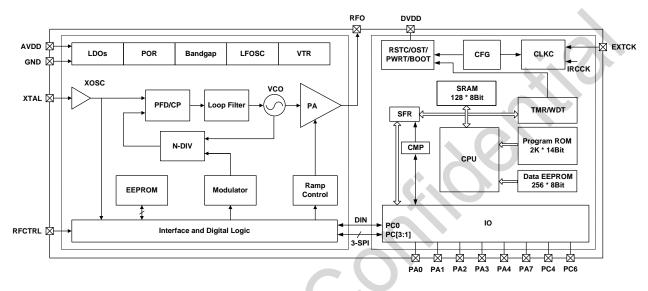

# 1.1 Overall Operating Principle

The CMT2189B is a RF transmitting chip integrated with digital and analog parts altogether, which applies a crystal oscillator to provide the reference frequency and digital clock for PLL, supporting OOK modulation with a data rate range of  $1 \sim 40$  kbps. It supports status control through the MCU programming to fulfill various low power transmission applications.

The chip adopts the PLL+PA architecture to achieve the Sub-GHz wireless transmission function with supports of FIFO packet mode and pass-through mode (in the FIFO packet mode, the embedded encoder allows users to select appropriate encoding formats). After the processed data is sent to the modulator (for the pass-through mode, data is not processed by the encoder but sent to the modulator directly after deburring), the modulator controls PLL and PA to have OOK modulation on the data and transmit the data after then.

By controlling the RF part through the 3-wire SPI interface, the MCU can control various status switching, mode selection and low power control.

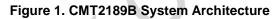

# 1.2 IO Pin Description

| Pin #    | Pin Name            | Туре    | I/O | Description                                                |                                                                 |  |

|----------|---------------------|---------|-----|------------------------------------------------------------|-----------------------------------------------------------------|--|

| 1        | DVDD                | Digital | I   | Chip power supply +                                        |                                                                 |  |

| 2        | PC6                 | Digital | ю   | General purpose                                            | e IO                                                            |  |

| 3        | PC4/C2OUT           | Digital | 10  | PC4                                                        | General purpose IO                                              |  |

|          |                     | Digital |     | C2OUT                                                      | Comparator 2 output                                             |  |

| 4        | XTAL                | Analog  | I   | Crystal oscillator                                         | r input in RF part                                              |  |

| 5        | RFCTRL              | Digital | I   | SPI interface en                                           | abling control in RF part, low active, internal pull up.        |  |

| 6        | AVDD                | Analog  | I   | RF part power s                                            | upply +                                                         |  |

| 7        | GND                 | Digital | -   | Chip power supp                                            | bly ground                                                      |  |

| 8        | RF0                 | Analog  | 0   | RF part PA outpo                                           | ut                                                              |  |

| 9        | PA4                 | Digital | Ю   | General purpose                                            | e IO with support of IOC and configurable pull-up               |  |

| 10       | PA3                 | Digital | ю   | General purpose                                            | e IO with support of IOC and configurable pull-up               |  |

|          |                     |         |     | PA2                                                        | General purpose IO with support of IOC and configurable pull-up |  |

| 11       | PA2/T0CKI/INT/C1OUT | Digital | ю   | тоскі                                                      | Timer 0 clock source input (Max=4MHz)                           |  |

|          |                     |         |     | INT                                                        | External interrupt input                                        |  |

|          |                     |         |     | C1OUT                                                      | Comparator 1 output                                             |  |

|          | PA0/C1IN+/ICSPCLK   | $\sim$  |     | PA0                                                        | General purpose IO with support of IOC and configurable pull-up |  |

| 12       |                     | Digital | ю   | C1IN+                                                      | Comparator 1 input +                                            |  |

|          | S                   |         |     | ICSPCLK                                                    | Serial port clock signal for debug/programming mode             |  |

|          |                     |         |     | PA1                                                        | General purpose IO with support of IOC and configurable pull-up |  |

| 13       | PA1/C1IN-/ICSPDAT   | Digital | ю   | C1IN-                                                      | Comparator 1 input -                                            |  |

|          |                     |         |     | ICSPDAT Serial port data signal for debug/programming mode |                                                                 |  |

|          | PA7/OSC1/CLKI       | Digital |     | PA7                                                        | General purpose IO with support of IOC and configurable pull-up |  |

| 14       |                     |         | Ю   | OSC1                                                       | MCU crystal pin                                                 |  |

|          |                     |         |     | CLKI                                                       | External clock input pin                                        |  |

| Internal |                     |         |     | PC0 General purpose IO                                     |                                                                 |  |

| pin      | PC0/C2IN+/RFDIN     | Digital | IO  | C2IN+                                                      | Comparator 2 input +                                            |  |

Table 2. CMT2189B Pin Description - SOP14 Package

| Pin #    | Pin Name       | Туре    | I/O | Description |                                                                                                                   |  |  |

|----------|----------------|---------|-----|-------------|-------------------------------------------------------------------------------------------------------------------|--|--|

|          |                |         |     | RFDIN       | RF data input pin for pass-through mode                                                                           |  |  |

|          |                |         |     | PC1         | General purpose IO, connecting RF part and chip internally                                                        |  |  |

| Internal | PC1/C2IN-/SDIO | Digital | 10  | C2IN-       | Comparator 1 output -                                                                                             |  |  |

| pin      | PC1/C2IN-/SDIO | Digital | IO  | SDIO        | 3-wire SPI serial bus data SDIO in RF part, which is a bidirectional port without pull-up or pull-down resistors. |  |  |

| Internal | PC2/SCLK       | Digital | 10  | PC2         | General purpose IO, connecting RF part and chip internally                                                        |  |  |

| pin      |                |         |     | SCLK        | 3-wire SPI serial bus clock SCLK in RF part                                                                       |  |  |

| Internal | PC3/CSB        | Digital | Ю   | PC3         | General purpose IO, connecting RF part and chip internally                                                        |  |  |

| pin      |                |         |     | CSB         | 3-wire SPI serial bus chip selection CSB in RF part with internal pull-up resistor                                |  |  |

#### Notes:

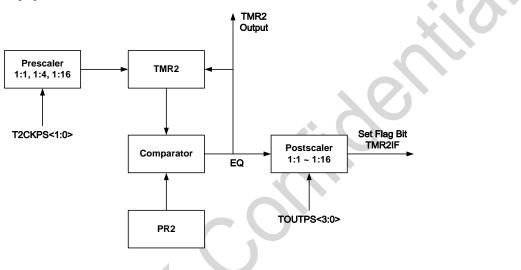

- 1. The MCU has 2 built-in comparators, but the 2 internal comparators cannot be used due to the pin packaging limitation and the multiplexing of RF part for some pins. However the MCU still needs to have necessary comparator settings after initialization to avoid impact on other functions.

- 2. The clock source system of the MCU supports both internal oscillations and external oscillations. The external oscillation supports dual-end crystal and single-end clock source input. However, due to the package pin limitation, the PA6 has no package pin, therefore it does not support the external oscillation mode per dual-end crystal, namely only the external oscillation mode per single-end clock source is supported.

- 3. PC<3:0> is the internal control pin of the chip, which has no package pin, but it is used as a bus controlling RF part internally.

# 2 RF Part Configuration and Control Mechanism

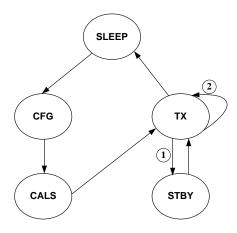

# 2.1 Operating Mode

The built-in OOK Tx function of the CMT2189B supports 2 operating modes.

- Simple operating mode: the default entry mode upon power-up, namely, the non-configuration mode, which supports the pass-through Tx mode only.

- Advanced configuration mode: it supports register configuration and operating state control through the SPI bus, which supports both the FIFO and pass-through Tx mode.

Notes:

1. The pass-through Tx input sources in the 2 operating modes are different. Please see more details in below Sections.

## 2.2 Simple Operating Mode

In the simple operating mode, the only peripheral required is a crystal oscillator. Upon power-up, the chip controls data transmission through the internal PC1 (SDIO) to fulfill data transmission at the corresponding frequency. In this mode, the frequency multiplier factor is fixed to 16.5, calculated based on the following formula.

where FXTAL is the crystal frequency and FRF is the target frequency, and the frequency range is 314 MHz ~ 480MHz.

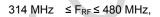

## Figure 3. Tx Timing Diagram in the Simple operating Mode

## Notes:

- 1. This mode supports a rate range of  $1 \sim 20$  kbps.

- 2. The maximum power output is fixed to +13 dBm. Users can reduce the Tx power by connecting a resistor to limit current before the chock inductor if it is needed.

- 3. The internal SPI bus does not need to send any control commands and only needs to hold PC<3:0> in a high resistance input status (except PC1).

- 4. The RFCTRL pin can be suspended in this mode.

- 5. In this mode, the data transmitting pin is PC1 (SDIO), which is set to 0 in the low power state (the normal state). When data transmitting is needed, it triggers on the rising edge to enter data transmitting state. After transmitting, PC1 is set to 0 and lasts for more than 20 ms (T<sub>OFF</sub> time), and RF exits from the Tx mode automatically to enter the low power state.

- 6. For this mode, in low power state, PC1/SDIO is set 0 to output and PC2/SCLK, PC3/CSB, and PC0/RFDIN are set to high resistance input.

# 2.3 Advanced Configuration Mode

To achieve higher performance and more functions such as the target operating frequency of 868MHz and chip automatic packet transmitting in transmission process, users need to use the advanced configuration mode with supports of the following features.

- Support more frequency multiplication factors to cover a frequency range of 240 ~ 960 MHz.

- By filling the FIFO and transmitting the message automatically (repeatedly, multiple times and periodically), it can release the MCU to do more work (In the pass-through mode, this process will take up MCU resource).

- Support more accurate Tx rates with the accuracy determined by crystal, which is excellent in accuracy (in the pass-through mode, the speed is controlled by the MCU software, and the accuracy depends on the software and the internal RC).

- Support voltage detection function inside RF, which offers simple power supply voltage detection and analysis judgment processing.

- Dynamical Tx power adjustment according to the power supply voltage to save power and prolong battery life.

In this mode, the chip internal MCU can have the RF mode control by operating registers through the 3-wire SPI (PC3/CSB, PC2/SCLK, PC1/SDIO) to fulfill the 2 Tx modes.

#### 1. Hardware packet Tx mode, which fills FIFO through SPI (see Section 2.9 for details)

The contents that need to be transmitted are filled into specified registers, which are automatically transmitted according to the speed, coding mode, number of packets and packet interval, etc.(the data package format and other relevant information are detailed in Section 2.7).

#### 2. Pass-through Tx mode using PC0/RFDIN as data pin (see Section 2.10 for details)

That is, the 1-Pin Tx mode, the data stream is generated by the MCU and output through the specified pin to fulfill the most elementary operating mode, namely *data pin in, antenna out*.

#### Notes:

- 1. The 2 Tx modes mentioned above are all in the advanced configuration mode, namely configuring and operating the chip through SPI.

- 2. In the advanced configuration mode, it is required to control RFCTRL through other pins, therefore the RFCTRL pin cannot be suspended.

- 3. The pass-through mode in the advanced configuration mode is similar to the pass-through mode in simple operating mode, namely they both control data transmitting through a data pin, however the data input sources are different. In simple operating mode, the Tx input pin is PC1/SDIO, while in the advanced configuration mode, it is changed to PC0/RFDIN because PC1/SDIO is used as the serial data line of SPI. With both using the register configuring method, the pass-through mode in advanced configuration mode can support more frequency selection and power selection than that in the simple operating mode.

# 2.4 SPI Interface Timing

The RF function inside the chip is controlled by a 3-wire SPI, and the corresponding relationship between SPI interface and the IO of the MCU is as follows.

| 3-wire SPI | MCU Control Port | Function                                                   |

|------------|------------------|------------------------------------------------------------|

| CSB        | PC3              | Bus chip selection enabling, low active, built-in pull-up. |

| SCLK       | PC2              | Bus clock line, triggering on the rising edge              |

| SDIO       | PC1              | Bi-directional bus data                                    |

#### Table 3. Relationship between SPI Bus and Control Port

#### Notes

- 1. SDIO, a bi-directional port, is used for data input and output. Both the address and data part are transmitted starting from MSB.

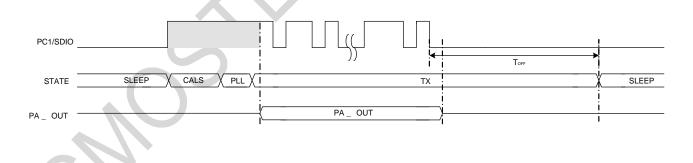

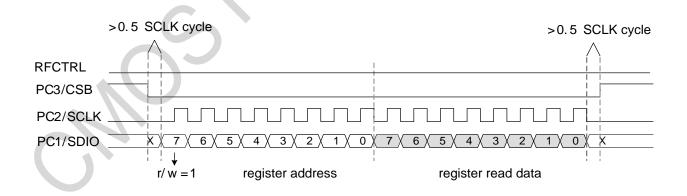

- 2. When the RF part is accessed, RFCTRL is pulled down[\*] to enable SPI serial port function, then the chip selection enabling (PC3/CSB) is pulled down and a R/W bit is sent followed by a 7-bit register address. After the chip selection enabling (PC3/CSB) is pulled down, it is necessary to wait for at least half a PC2 (SCLK) cycle to start sending R/W bit. After sending the falling edge of the last PC2 (SCLK), the chip must wait for at least half a SCLK cycle, and then pull the PC3 (CSB) high.

- 3. In the SPI read operation as shown in the below figure, please pay special consideration on PC1/SDIO, since SDIO is a bi-directional port, which will switch from the input state to the output state on the falling edge of the 8<sup>th</sup> clock (the dotted line in the middle of the figure below), and SDIO needs to switch from the output state to the input state before the falling edge of the 8<sup>th</sup> clock.

Figure 4. SPI Read Register Timing

Figure 5. SPI Write Register Timing

#### Notes

RFCTRL is an input port requiring external control. It is recommended that users control it through any function port in the CMT2189B, and pull it down to enable SPI interface function. In the whole process, RFCTRL can keep low, but in the low power sleep mode, it needs to set the MCU pin controlling RFCTRL to a high impedance input, since the pull-up inside RFCTRL can pull the level high. Do not set the MCU pin to low output, since pull-down will consume power.

## 2.5 RF Configuration Parameter

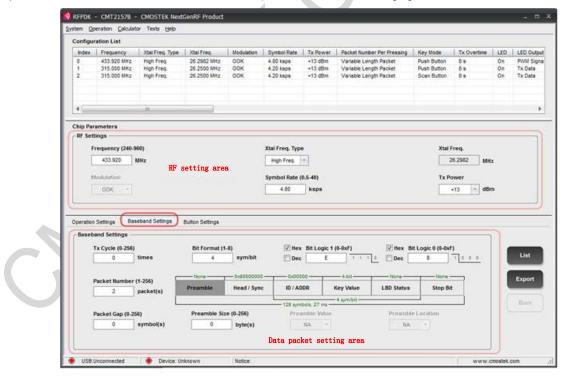

When the CMT2189B operates in the advanced configuration mode, it can achieve a more wide operating frequency range, packet format, etc. These functions require corresponding configuration parameters, which can be exported by the RFPDK software. The operating process is: open the RFPDK software and select the CMT2157B model (it has the same specifications and performance with the built-in RF of the CMT2189B), as shown in the following figure.

Figure 6. RFPDK Screen for CMT2157B

In the UI screen, there are mainly 2 areas: RF parameter settings area and data packet settings area. Users have configuration based on requirements according to the relevant registers described below, and then click *Export* to generate an exp file with file content as follows.

| ;                                                      |   |

|--------------------------------------------------------|---|

| ; CMT2157B Configuration File                          |   |

| ; Generated by CMOSTEK RFPDK 1.46                      |   |

| ; 2017.11.14 13:47                                     |   |

| ;                                                      | Þ |

| ; (Among them, the annotation part with ; is omitted.) |   |

| ;                                                      |   |

| ; The following are the EEPROM contents                |   |

| ·                                                      |   |

| 0x7E4F                                                 |   |

| 0x2134                                                 |   |

| 0x017F                                                 |   |

| 0x8015                                                 |   |

| 0x0018                                                 |   |

| 0x7F00                                                 |   |

| 0x0000                                                 |   |

| 0x8000                                                 |   |

| 0x0000                                                 |   |

| 0x0000                                                 |   |

| 0xA073                                                 |   |

| 0xE080                                                 |   |

| 0x2010                                                 |   |

| 0x8040                                                 |   |

| 0x5030                                                 |   |

| 0x6090                                                 |   |

| 0xC0A0                                                 |   |

| 0x0000                                                 |   |

| 0x0100                                                 |   |

| 0x027C                                                 |   |

| 0x957B                                                 |   |

0x70F0

0x0083

0x0000

; The following is the CRC result for

\_\_\_\_\_

; the above EEPROM contents

;-----

0xEDFA

;-----

; The following are for CMOSTEK

; use, customers can ignore them

;-----

0x0000

0x0018

Among them, the specific configuration content is with red font, which are all 16-bit Word with a total of 24 Words contained, therefore users need to convert the 16-bit Word to the format of 8-bit register content. The conversion method is that the higher 8-bit of each 16-bit Word is an odd number address and the lower 8-bit is an even address. The conversion of 24 Words gets 48 register configuration values with an address range of 0x00 ~ 0x2E (the last 8-bit is invalid). According to the above file, the obtained register contents are as follows.

|   | 16-Bit Word | Register Address | 8-bit Register Configuration Value |  |  |

|---|-------------|------------------|------------------------------------|--|--|

| - | 0x7E4F      | 0x00             | 0x4F                               |  |  |

|   | UX/E4F      | 0x01             | 0x7E                               |  |  |

|   | 0x2134      | 0x02             | 0x34                               |  |  |

|   | 0x2134      | 0x03             | 0x21                               |  |  |

|   | 0x017F      | 0x04             | 0x7F                               |  |  |

|   | UXU17F      | 0x05             | 0x01                               |  |  |

|   | 0.0045      | 0x06             | 0x15                               |  |  |

|   | 0x8015      | 0x07             | 0x80                               |  |  |

|   | 0x0018      | 0x08             | 0x18                               |  |  |

|   | 0x0018      | 0x09             | 0x00                               |  |  |

|   | 0x7F00      | 0x0A             | 0x00                               |  |  |

|   | UX/FUU      | 0x0B             | 0x7F                               |  |  |

|   | 0x0000      | 0x0C             | 0x00                               |  |  |

|   | 0x0000      | 0x0D             | 0x00                               |  |  |

|   | 0x8000      | 0x0E             | 0x00                               |  |  |

|   | 0.0000      | 0x0F             | 0x80                               |  |  |

## Table 4. Conversion Table from 16-bit EEPROM Word to 8-bits Register Content

| 16-Bit Word | Register Address | 8-bit Register Configuration Value |

|-------------|------------------|------------------------------------|

| 0,0000      | 0x10             | 0x00                               |

| 0x0000      | 0x11             | 0x00                               |

| 0.0000      | 0x12             | 0x00                               |

| 0x0000      | 0x13             | 0x00                               |

| 0.4072      | 0x14             | 0x73                               |

| 0xA073      | 0x15             | 0xA0                               |

| 0.2000      | 0x16             | 0x80                               |

| 0xE080      | 0x17             | 0xE0                               |

| 0.2010      | 0x18             | 0x10                               |

| 0x2010      | 0x19             | 0x20                               |

| 0.2040      | 0x1A             | 0x40                               |

| 0x8040      | 0x1B             | 0x80                               |

| 0           | 0x1C             | 0x30                               |

| 0x5030      | 0x1D             | 0x50                               |

| 0x6090      | 0x1E             | 0x90                               |

|             | 0x1F             | 0x60                               |

| 0xC0A0      | 0x20             | 0xA0                               |

| UXCUAU      | 0x21             | 0xC0                               |

| 0,0000      | 0x22             | 0x00                               |

| 0x0000      | 0x23             | 0x00                               |

| 0.0100      | 0x24             | 0x00                               |

| 0x0100      | 0x25             | 0x01                               |

| 0x027C      | 0x26             | 0x7C                               |

| 0x027C      | 0x27             | 0x02                               |

| 0x957B      | 0x28             | 0x7B                               |

| 089576      | 0x29             | 0x95                               |

| 0.7050      | 0x2A             | 0xF0                               |

| 0x70F0      | 0x2B             | 0x70                               |

| 0×0083      | 0x2C             | 0x83                               |

| 0x0083      | 0x2D             | 0x00                               |

| 0x0000      | 0x2E             | 0x00                               |

Users only need to write the above contents (as parameters) into the  $0x01 \sim 0x2E$  register address while writing timing through SPI.

# 2.6 Configuration Register

The above exported configuration parameter address from 0x01 to 0x2E can be divided into three banks according to the functions, which are as follows:

| Bank        | Address     | Involved Content                                          |  |  |

|-------------|-------------|-----------------------------------------------------------|--|--|

| Tx Bank     | 0x00 – 0x03 | Tx frequency, Tx power                                    |  |  |

| Packet Bank | 0x04 – 0x27 | Tx rate, packet format (only for hardware packet Tx mode) |  |  |

| System Bank | 0x28 – 0x2E | System parameters                                         |  |  |

### Table 5. Configuration Register Area Partition Table

#### • Tx Bank

Tx bank parameter association is as follows.

The register address range is  $0x00 \sim 0x03$ . These parameters are majorly about Tx central frequency and Tx power. When users need to transmit with multiple frequencies in applications, such as frequency hopping or adjusting Tx power according to voltage value, they can export different parameter tables after setting in the RFPDK, and it only need to take the segment in  $0x00 \sim 0x03$ . The detailed register description is not discussed here.

#### Packet Bank

The register address range associated with packet bank parameters is  $0x04 \sim 0x27$ . These parameters are mainly setting items about hardware packet format, applicable to the hardware packet Tx mode only. Please refer to Chapter 2.7 for detailed register description.

#### • System Bank

The register address range associated with the system bank parameters is 0x28~0x2E. These parameters are the specific parameters for RF, not related to user applications. Users can configure them according to the parameters exported from RFPDK with no need to care about the details. Details will not be discussed here.

## 2.7 Packet Related Register

An overview of the packet bank register is shown in the below table.

| Addr | Name     | Bit 7     | Bit 6              | Bit 5   | Bit 4  | Bit 3         | Bit 2             | Bit 1           | Bit 0      |  |  |

|------|----------|-----------|--------------------|---------|--------|---------------|-------------------|-----------------|------------|--|--|

| 0x04 | CUS_DIG1 |           | SYMBOL_TIME<7:0>   |         |        |               |                   |                 |            |  |  |

| 0x05 | CUS_DIG2 |           | SYMBOL_TIME<15:8>  |         |        |               |                   |                 |            |  |  |

| 0x06 | CUS_DIG3 |           |                    |         |        | LBD_TH<3:0>   |                   | LBD_OUT_EN      | LBD_ON     |  |  |

| 0x07 | CUS_DIG4 |           |                    |         |        | DEGLITCH_EN   | тх                | _OVERTIMES<2:0> |            |  |  |

| 0x08 | CUS_PKT1 | TCYCLE_EN | INTERVAL EN        | STOP EN | KEY EN | SYNC EN       | PREAMBLE LOCATION | PREAMBLE SEL    | PREAMBLE_E |  |  |

| 0x08 | CUS_PKIT | TOTOLE_EN | INTERVAL_EN        | STOP_EN |        | STNC_EN       | PREAMBLE_LOCATION | PREAMDLE_SEL    | Ν          |  |  |

| 0x09 | CUS_PKT2 |           |                    |         |        | TXCYCLE<7:    | 0>                |                 |            |  |  |

| 0x0A | CUS_PKT3 |           |                    |         |        | PREAMBLE_LENG | TH<7:0>           |                 |            |  |  |

| 0x0B | CUS_PKT4 | к         | EY_LENGTH<2:0>     |         |        |               | SYNC_LENGTH<4:    | )>              |            |  |  |

| 0x0C | CUS_PKT5 |           |                    |         |        | SYNC_HEADER   | <7:0>             |                 |            |  |  |

| 0x0D | CUS_PKT6 |           |                    |         |        | SYNC_HEADER   | <15:8>            |                 |            |  |  |

| 0x0E | CUS_PKT7 |           | SYNC_HEADER<23:16> |         |        |               |                   |                 |            |  |  |

| 0x0F | CUS_PKT8 |           | SYNC_HEADER<31:24> |         |        |               |                   |                 |            |  |  |

| 0x10 | CUS_PKT9 |           |                    |         |        | ADDR_ID<7:    | )>                |                 |            |  |  |

## Table 6. Packet Bank Register Overview

| Addr   | Name      | Bit 7 | Bit 6            | Bit 5 | Bit 4 | Bit 3          | Bit 2               | Bit 1             | Bit 0      |  |  |  |  |

|--------|-----------|-------|------------------|-------|-------|----------------|---------------------|-------------------|------------|--|--|--|--|

| 0x11   | CUS_PKT10 |       | ADDR_ID<15:8>    |       |       |                |                     |                   |            |  |  |  |  |

| 0x12   | CUS_PKT11 |       |                  |       |       | ADDR_ID<23:    | 16>                 |                   |            |  |  |  |  |

| 0x13   | CUS_PKT12 |       |                  |       |       | ADDR_ID<31:    | 24>                 |                   |            |  |  |  |  |

| 0x14   | CUS_PKT13 | E     | BIT_FORMAT<2:0>  |       |       |                | ADDR_LENGTH<4:      | :0>               |            |  |  |  |  |

| 0x15   | CUS_PKT14 |       | STOP_LENGTH<3:0> |       |       |                |                     |                   |            |  |  |  |  |

| 0x16   | CUS_PKT15 |       | BIT_LOGIC_L<7:0> |       |       |                |                     |                   |            |  |  |  |  |

| 0x17   | CUS_PKT16 |       | BIT_LOGIC_H<7:0> |       |       |                |                     |                   |            |  |  |  |  |

| 0x18   | CUS_PKT17 |       | KEY<7:0>         |       |       |                |                     |                   |            |  |  |  |  |

| 0x19   | CUS_PKT18 |       |                  |       |       |                |                     |                   |            |  |  |  |  |

| ~      | ~         |       |                  |       |       |                |                     |                   |            |  |  |  |  |

| 0x21   | CUS_PKT26 |       |                  |       |       |                |                     |                   |            |  |  |  |  |

| 0x22   | CUS_PKT27 |       |                  |       |       | STOP_BIT_L<    | 7:0>                |                   |            |  |  |  |  |

| 0x23   | CUS_PKT28 |       |                  |       |       | STOP_BIT_H<1   | 5:8>                |                   |            |  |  |  |  |

| 0x24   | CUS_PKT29 |       |                  |       |       | INTERVAL_LENGT | <sup>-</sup> H<7:0> |                   |            |  |  |  |  |

| 0x25   | CUS_PKT30 |       |                  |       |       | PKT_NUM<7:     | 0>                  |                   |            |  |  |  |  |

| 0x26   | CUS_RESV1 |       |                  |       |       |                |                     |                   |            |  |  |  |  |

| 0x27   | CUS_RESV2 |       |                  |       |       |                |                     | INTERVAL_STBY_DIS | STBY_PLLOF |  |  |  |  |

| 0,72,1 | 000_RE0V2 |       |                  |       |       |                |                     | INTERVAL_STBT_DIS | F_DIS      |  |  |  |  |

#### Notes

- The gray area indicates it has content but users do not need to understand it. Users only need to configure them according to the parameters exported from RFPDK. Users need follow the procedure of *read-modify-write* to set an individual bit to 1 or 0.

- 2. The blue area indicates that users need to understand it. The registers will be detailed one by one in below.

- 3. The built-in packet structure pattern of the CMT2189B is the same as that of the CMT2157B. Users can select the packet structure of the CMT2157B in RFPDK configuration screen. The configuration parameters generated in *exp* are arranged according to required format and order. Users only need to fill in the specific data content during software executing.

## 2.7.1 Tx Rate

The Tx rate is determined by SYMBOL\_TIME<15:0> and can be generated by RFPDK.

|                 |      |     | •                 |                               |  |  |

|-----------------|------|-----|-------------------|-------------------------------|--|--|

| Register Name   | Bits | R/W | Bit Name          | Function description          |  |  |

| CUS_DIG1 (0x04) | 7:0  | RW  | SYMBOL_TIME<7:0>  | Tx data rate of Packet format |  |  |

| CUS_DIG2 (0x05) | 7:0  | RW  | SYMBOL_TIME<15:8> | TX data fate of Packet format |  |  |

#### Table 7. Tx Rate Related Register

## 2.7.2 Hardware Packet Format

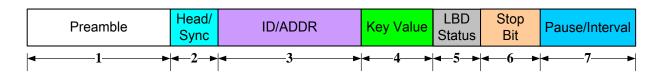

The CMT2189B supports hardware packet structure internally with data frame structure as follows.

As shown in the packet structure in the above figure, it contains 7 parts.

- 1. Preamble: optional, the value can be selected as 0x55 or 0xAA<sup>[1]</sup>, ranging from 0 to 256 bytes (select any value within the range).

- 2. Head/Sync: synchronous word, optional, ranging from 0 to 32 bit<sup>s[2]</sup> (select any value within the range).

- 3. ID/ADDR: sequence number, mandatory, ranging from 1 to 32 logic bits<sup>[3]</sup> (select any value within the range).

- 4. Key value: optional, ranging from 0 to 8 logic bits<sup>[3]</sup> (select any value within the range).

- 5. LBD status: low battery detection status bit, optional, occupying 1 logic bit <sup>[3]</sup>;

- 6. Stop bit: optional, ranging from  $0 \sim 16$  bits<sup>[2]</sup> (select any value within the range).

- 7. Packet interval, fixed to send 0, ranging from  $0 \sim 256$  bit<sup>s[2]</sup>;

#### Notes:

- [1]. Preamble adopts NRZ format without encoding, e.g. for 0x55, the data flow is 0b01010101 at the set rate (0 represents low level and 1 represents high level).

- [2]. Head/Sync, stop bit and pause/interval will not be encoded. They are output at the set rate just like the preamble code.

- [3]. Logic bits, representing the encoded bits, which are described in detail below. Item 3 ~ 5 in the message structure as shown in the above figure all supports being encoded by the internal encoder.

For example, the coding rules choose at least 1 symbol as 1 logical bit, that is, 0b0 is logic 0, and 0b1 is logic 1 (NRZ encoding) with following settings.

Preamble: set to open. The value is 0xAA with a length of 5 bytes.

Head/Sync: set to open. The value is 0x2DD4 with a length is 2 bytes.

ID/ADDR: the value is 0x12345678 with a length of 4 bytes.

Key Value: the value is 0x9A.

LBD Status: set to close.

Stop bit: set to open. The value is 0xBCDE with a length of 16 bits (2 bytes).

Pause/interval: pause/interval: set to open. The length is 32 bits (4 bytes).

Then the data flow is as follows.

0xAA AA AA AA AA AA 2D D4 12 34 56 78 9A BC DE 00 00 00 00 AA AA AA AA AA AA 2D D4 12 34 56 78 9A BC DE 00...

## 2.7.3 Preamble

| Register<br>Name   | Bits | R/W            | Bit Name                 | Function Description                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|------|----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CUS_PKT1           | 2    | RW             | PREAMBLE_LOCATION        | <ul> <li>When enabling Tcycle, it represents the preamble location in the packet structure of:</li> <li>0: in one cycle, each packet contains 1 preamble, e.g. there are N packets in the 1 cycle, which contain N preambles.</li> <li>1: in one cycle, it only contains 1 preamble, and it is in the first packet only.</li> <li>Note: the concept of Tcycle is described in detail later.</li> </ul> |

| (0x08)             | 1    | RW             | PREAMBLE_SEL             | Preamble selection bit.<br>0: 0x55<br>1: 0xAA                                                                                                                                                                                                                                                                                                                                                          |

|                    | 0    | RW PREAMBLE_EN |                          | Preamble enabling bit.<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                      |

| CUS_PKT3<br>(0x0A) | 7:0  | RW             | PREAMBLE_LENGTH<7:<br>0> | The length of preamble can be configured to a value in 0~255.<br><i>O</i> represents that sending 1 byte of Preamble, and so on. 255<br>represents that it sends preamble with 256 bytes.                                                                                                                                                                                                              |

## Table 8. Preamble Configuration Register

For users, if the PREAMBLE\_EN is 0, a preamble is not sent, and if the configuration is 1, a preamble with 1 ~ 256 bytes is sent.

## 2.7.4 Head/Sync

## Table 9. Head/Sync Configuration Register

| Register<br>Name   | Bits          | R/W | Bit Name           | Function Description                                                                                                                                                                        |  |  |

|--------------------|---------------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CUS_PKT1<br>(0x08) | 3             | RW  | SYNC_EN            | Sync enabling bit.<br>0: disable<br>1: enable                                                                                                                                               |  |  |

| CUS_PKT4<br>(0x0B) | 4:0           | RW  | SYNC_LENGTH<4:0>   | The sync length can be configured as 0 ~ 31. 0 represents sending a sync with 1 symbol and so on. <i>31</i> represents sending a sync with <i>32</i> symbols. A symbol is random in length. |  |  |

| CUS_PKT5<br>(0x0C) | 7:0           | RW  | SYNC_HEADER<7:0]>  |                                                                                                                                                                                             |  |  |

| CUS_PKT6<br>(0x0D) | (0x0D) 7:0 RW |     | SYNC_HEADER<15:8>  | The value of sync can be filled in different registers according to the different SYNC_LENGTH settings,                                                                                     |  |  |

| CUS_PKT7<br>(0x0E) |               |     | SYNC_HEADER<23:16> | please refer the next table for details.                                                                                                                                                    |  |  |

| CUS_PKT8           | 7:0           | RW  | SYNC_HEADER<31:24> |                                                                                                                                                                                             |  |  |

| (0x0F) |  |  |

|--------|--|--|

#### Table 10. Relationship between Head/Sync Length Selection and Register

|             |              | SYNC/HEADER  |              |       |  |  |  |  |  |  |  |  |

|-------------|--------------|--------------|--------------|-------|--|--|--|--|--|--|--|--|

| SYNC_LENGTH | <31:24>      | <23:16>      | <15:8>       | <7:0> |  |  |  |  |  |  |  |  |

| 0~7         | $\checkmark$ |              |              |       |  |  |  |  |  |  |  |  |

| 8~15        | $\checkmark$ | $\checkmark$ |              |       |  |  |  |  |  |  |  |  |

| 16~23       | $\checkmark$ | $\checkmark$ | $\checkmark$ |       |  |  |  |  |  |  |  |  |

| 24~31       | $\checkmark$ | $\checkmark$ | $\checkmark$ | V     |  |  |  |  |  |  |  |  |

In the table, tick indicates a register to be filled. For example, if SYNC\_LENGTH is set to 15, that is, the length is 16 symbols and sync value is 0x5678, then users will fill the value into SYNC\_HEADER<31:24> and SYNC\_HEADER<23:16> registers. MSB corresponds to the 31<sup>st</sup> bit and LSB corresponds to the 16<sup>th</sup> bit, that is, 0x56 is filled into SYNC\_HEADER<31:24> and 0x78 is filled into SYNC\_HEADER<23:16>. For users, if the sync enabling bit is 0, a sync is not sent, and if the sync enabling bit is 1, a sync of 1-32 symbols is sent.

## 2.7.5 Addr/ID

| Register<br>Name    | Bits           | R/W | Bit Name         | Function Description                                                                                                                                                                            |  |  |  |  |

|---------------------|----------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CUS_PKT13<br>(0x14) | 4:0            | RW  | ADDR_LENGTH<4:0> | The Addr ID length can be configured to 0 ~ 31. 0<br>represents sending an Addr of 1 logic bit, and so on. 31<br>represents sending an Addr of 32 logic bits.The logic bit<br>length is random. |  |  |  |  |

| (0,14)              | 7:5            | RW  | BIT_FORMAT<2:0>  | The number of symbol that is contained by 1 logic bit can<br>be configured to 0 ~ 7. 0 represents 1 symbol and so on.<br>7 represents 8 symbols.                                                |  |  |  |  |

| CUS_PKT15<br>(0x16) | 7:0            | RW  | BIT_LOGIC_L<7:0> | Logic 0 definition                                                                                                                                                                              |  |  |  |  |

| CUS_PKT16<br>(0x17) | 7:0            | RW  | BIT_LOGIC_H<7:0> | Logic 1definition                                                                                                                                                                               |  |  |  |  |

| CUS_PKT9<br>(0x10)  | 7:0            | RW  | ADDR_ID<7:0>     |                                                                                                                                                                                                 |  |  |  |  |

| CUS_PKT10<br>(0x11) | 7:0            | RW  | ADDR_ID<15:8>    | Addr ID value                                                                                                                                                                                   |  |  |  |  |

| CUS_PKT11<br>(0x12) | 7:0            | RW  | ADDR_ID<23:16>   |                                                                                                                                                                                                 |  |  |  |  |

| CUS_PKT12<br>(0x13) | 7:0 RW ADDR_ID |     | ADDR_ID<31:24>   |                                                                                                                                                                                                 |  |  |  |  |

## Table 11. Addr/ID Related Registers

|             |              | ADDR_ID      |              |              |  |  |  |  |  |  |  |  |

|-------------|--------------|--------------|--------------|--------------|--|--|--|--|--|--|--|--|

| ADDR_LENGTH | [31:24]      | [23:16]      | [15:8]       | [7:0]        |  |  |  |  |  |  |  |  |

| 0~7         | $\checkmark$ |              |              |              |  |  |  |  |  |  |  |  |

| 8~15        | $\checkmark$ | $\checkmark$ |              |              |  |  |  |  |  |  |  |  |

| 16~23       | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |  |  |  |  |  |  |  |  |

| 24~31       | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |  |  |  |  |  |  |  |

## Table 12. Relationship between Addr/ID Length Selection and Register

In the table, tick indicates a register to be filled. For example, If ADDR\_LENGTH is set to 15, the length is 16 logic bits and the value is 0x5678. Then users will fill the value into ADDR\_ID<31:24> and ADDR\_ID<23:16> registers. MSB is corresponding to the  $31^{st}$  bit and LSB corresponds to the  $16^{th}$  bit, that is, 0x56 is filled into ADDR\_ID<31:24> and 0x78 is filled into ADDR\_ID<23:16>.

|              | BIT_LOGIC_L/ BIT_LOGIC_H                            |                                                                                                                                                                                 |              |              |   |   |   |  |  |  |  |  |  |

|--------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---|---|---|--|--|--|--|--|--|

| 7            | 6                                                   | 5                                                                                                                                                                               | 4            | 3            | 2 | 1 | 0 |  |  |  |  |  |  |

| $\checkmark$ |                                                     |                                                                                                                                                                                 |              |              |   |   |   |  |  |  |  |  |  |

| $\checkmark$ | $\checkmark$                                        |                                                                                                                                                                                 |              |              |   |   |   |  |  |  |  |  |  |

| $\checkmark$ | $\checkmark$                                        | $\checkmark$                                                                                                                                                                    |              |              |   |   |   |  |  |  |  |  |  |

| $\checkmark$ | $\checkmark$                                        | $\checkmark$                                                                                                                                                                    | $\checkmark$ |              |   |   |   |  |  |  |  |  |  |

| $\checkmark$ | $\checkmark$                                        | $\checkmark$                                                                                                                                                                    | $\checkmark$ | $\checkmark$ |   |   |   |  |  |  |  |  |  |

| $\checkmark$ | $\checkmark$                                        | $\checkmark$                                                                                                                                                                    | $\checkmark$ | $\checkmark$ |   |   |   |  |  |  |  |  |  |

| $\checkmark$ | $\checkmark$                                        | $\checkmark$                                                                                                                                                                    | $\checkmark$ | $\checkmark$ |   | V |   |  |  |  |  |  |  |

| $\checkmark$ | $\checkmark$                                        | $\checkmark$                                                                                                                                                                    | $\checkmark$ | $\checkmark$ |   | V | V |  |  |  |  |  |  |

|              | 7<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | 7     6       √     √       √     √       √     √       √     √       √     √       √     √       √     √       √     √       √     √       √     √       √     √       √     √ |              |              |   |   |   |  |  |  |  |  |  |

## Table 13. Relationship between Encoding Length Selection and Bit Enabling

In the table, tick indicates a register to be filled. For example, if BIT\_FORMAT is set to 3, it represents 1 logic bit containing 4 symbols. If logic 0= 0b'1000', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'1110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'1110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'1110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'1110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'1110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the value into BIT\_LOGIC\_L<7:4>. If Logic 1= 0b'110', then users will fill the v

Associating the above example, if ADDR\_LENGTH is set to 20, ADDR\_ID<31:12> is 0x56789, BIT\_FORMAT is set to 4, BIT\_LOGIC\_L<7:4> is 0b '1000' and BIT\_LOGIC\_H<7:4> is 0b '1110'. Expand ADDR\_ID as symbol, then the Tx data is as follows.

| 波形  |       |      |       |        |        |       |      | 1     |       |      |       |       |        |       |       |        |        |      |       |      |

|-----|-------|------|-------|--------|--------|-------|------|-------|-------|------|-------|-------|--------|-------|-------|--------|--------|------|-------|------|

| 数据流 | 1000_ | 1110 | _1000 | _1110_ | _1000_ | 1110_ | 1110 | _1000 | _1000 | 1110 | _1110 | _1110 | _1110_ | _1000 | _1000 | _1000_ | _1110_ | 1000 | _1000 | 1110 |

| 二进制 | "0"   | "1"  | "0"   | "1"    | "0"    | "1"   | "1"  | "0"   | "0"   | "1"  | "1"   | "1"   | "1"    | "0"   | "0"   | "0"    | "1"    | "0"  | "0"   | "1"  |

| Hex |       |      | 5     |        |        | e     | 5    |       |       | -    | 7     |       |        |       | 8     |        |        | ġ    | ð     |      |

## Figure 2-6. ADDR ID Example Diagram

That is, ID/ADDR = 0h '8E8E\_8E8E\_8E8E\_E888\_E88E', a total of 80 symbols, transmitted starting from the higher bit.

## 2.7.6 Key Value

| Register Name    | Bits | R/W | Bit Name        | Function Description                                                                                                                                                             |

|------------------|------|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CUS_PKT1 (0x08)  | 4    | RW  | KEY_EN          | Key enabling bit.<br>0: disable<br>1: enable                                                                                                                                     |

| CUS_PKT4 (0x0B)  | 7:5  | RW  | KEY_LENGTH<2:0> | The key value length can be configured to 0~7. 0 represents sending a key of 1 logic bit, and so on. 7 represents sending a Key of 8 logic bits. The logic bit length is random. |

| CUS_PKT17 (0x18) | 7:0  | RW  | KEY<7:0>        | Key Value                                                                                                                                                                        |

#### Table 14. Key Value Configuration Register

The maximum length of the corresponding key value in the packet structure can be configured to 8, and the location of the tick in the table indicates the corresponding value of register to be filled. For example, if the KEY\_LENGTH is set to 3, that is, the length is 4 logic bits and the value is 0x5, users will fill the value into KEY0<7:4>. For configuring logic bit as symbol, please refer to the description of Addr ID.

Table 15. Relationship between Key Value Length Selection and Bit Enabling

|            |              | KEY Value    |              |              |              |              |              |              |  |  |  |  |  |  |  |

|------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--|--|--|--|--|--|--|

| KEY_LENGTH | Bit7         | Bit6         | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0         |  |  |  |  |  |  |  |

| 0          | $\checkmark$ |              |              |              |              |              |              | 0            |  |  |  |  |  |  |  |

| 1          | $\checkmark$ | $\checkmark$ |              |              |              |              |              |              |  |  |  |  |  |  |  |

| 2          |              | $\checkmark$ | $\checkmark$ |              |              |              |              |              |  |  |  |  |  |  |  |

| 3          |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | X            | 5            |              |  |  |  |  |  |  |  |

| 4          | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | V            | 0            |              |              |  |  |  |  |  |  |  |

| 5          |              | $\checkmark$ | $\checkmark$ | $\checkmark$ | V            | $\checkmark$ |              |              |  |  |  |  |  |  |  |

| 6          |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ |              |  |  |  |  |  |  |  |

| 7          | $\checkmark$ |  |  |  |  |  |  |  |

For users, if the KEY\_EN is 0, the key value is not sent. If the configuration is 1, the key value of 1~ 8 logic bits is sent.

## 2.7.7 LBD Status Configuration

Table 16. LBD Status Configuration Register

| Register Name            | Bits | R/W | Bit Name        | Function Description                                                                                                                                                          |

|--------------------------|------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | 0    | RW  | LBD_ON          | LBD (low battery detection) enabling bit.<br>0: disable<br>1: enable                                                                                                          |

| CUS_DIG3<br>(0x06)       | 1    | RW  | LBD_OUT_EN      | LBD output enabling bit (whether or not it is added<br>to the message)<br>0: disable<br>1: enable                                                                             |

|                          | 5:2  | RW  | LBD_TH<3:0>     | The voltage comparison threshold of the LBD. lif<br>the actual voltage is greater than the threshold, the<br>LBD result is 1 (logic 1), and conversely, it is 0<br>(logic 0). |

| CUS_LBD_RESULT<br>(0x4B) | 3:0  | R   | LBD_RESULT<3:0> | Voltage measurement value                                                                                                                                                     |

#### Notes

- 1. CUS\_LBD\_RESULT register is a functional register, which is not not a parameter exported through the RFPDK, see Section 2.8 for details.

- 2. The operating principle of LBD is: the chip compares the voltage value LBD\_TH set by users (threshold of LBD) with the actual voltage value LBD\_RESULT got by the test; if LBD\_RESULT is smaller than LBD\_TH, it indicates the low voltage occurs, on the contrary, it is the normal voltage. According to the comparison result, the LBD indicating signal will be output internally. If LBD\_OUT\_EN is configured as 1, the LBD result will be sent out as part of the packet. See Section 2.7.1 for details.

- 3. In the chip, the voltage value is converted by a 4-bit ADC to obtain LBD\_RESULT with each step as 0.2 V. The relationship between the voltage value and LBD\_RESULT is as follows.

|     |               | • •                            |

|-----|---------------|--------------------------------|

| NUM | LBD_TH        | LBD_TH<3:0> or LBD_RESULT<3:0> |

| 1   | <1.45 V       | 4'b0000                        |

| 2   | 1.45 ~ 1.65 V | 4'b0001                        |

| 3   | 1.65 ~ 1.85 V | 4'b0010                        |

| 4   | 1.85 ~ 2.05 V | 4'b0011                        |

| 5   | 2.05 ~ 2.25 V | 4'b0100                        |

| 6   | 2.25 ~ 2.45 V | 4'b0101                        |

| 7   | 2.45 ~ 2.65 V | 4'b0110                        |

| 8   | 2.65 ~ 2.85 V | 4'b0111                        |

| 9   | 2.85 ~ 3.05 V | 4'b1000                        |

| 10  | 3.05 ~ 3.25 V | 4'b1001                        |

| 11  | 3.25 ~ 3.45 V | 4'b1010                        |

| 12  | 3.45 ~ 3.65 V | 4'b1011                        |

| 13  | 3.65 ~ 3.85 V | 4'b1100                        |

| ≥14 | >3.85         | 4'b1101                        |

|     |               |                                |

## Table 17. LBD\_TH Configuration Register

#### Notes

- 1. LBD is not tested in real time, but is tested once after PLL frequency calibration. Therefore users need to switch to STBY status first and then switch to Tx status to trigger the measurement process.

- 2. LBD\_RESULT can be used as a condition for judgment. Therefore users can use LBD\_RESULT as a quantitative analysis after triggering the LBD condition.

## 2.7.8 Stop Bit Configuration

| Table 18 | Stop | Bit Configuration | Register |

|----------|------|-------------------|----------|

|----------|------|-------------------|----------|

| Register Name | Bits | R/W  | Bit Name         | Function Description                                 |

|---------------|------|------|------------------|------------------------------------------------------|

| CUS_PKT1      |      |      |                  | Stop bit enabling bit.                               |

| (0x08)        | 5    | RW   | STOP_EN          | 0: disable                                           |

| (0x08)        |      |      |                  | 1: enable                                            |

|               |      |      |                  | The stop bit length can be configured to 0 ~ 15. 0   |

| CUS_PKT14     | 3:0  | RW   | STOP_LENGTH<3:0> | represents sending a stop of 1 Symbol, and so on. 15 |

| (0x15)        | 3.0  |      |                  | represents sending a stop of16 symbols, The symbol   |

|               |      |      |                  | length is random.                                    |

| CUS_PKT27     | 7:0  | RW   | STOP BIT<7:0>    |                                                      |

| (0x22)        | 7.0  |      |                  | STOP_BIT Value                                       |

| CUS_PKT28     | 7:0  | RW   | STOP BIT<15:8>   |                                                      |

| (0x23)        | 7.0  | IXVV | 310F_01110.02    |                                                      |

|             | STOP_BIT     |              |  |  |

|-------------|--------------|--------------|--|--|

| STOP_LENGTH | <15:8>       | <7:0>        |  |  |

| 0~7         | $\checkmark$ |              |  |  |

| 8~15        | $\checkmark$ | $\checkmark$ |  |  |

### Table 19. Relationship between Stop Bit Length Selection and Bit Enabling

In the table, tick indicates a register to be filled. For example, if STOP\_LENGTH is set to 7, that is, the length is 8 symbols, and the value is 0x56. Then users will fill this value into STOP\_BIT[15:8]. MSB corresponds to the 15<sup>th</sup> bit, and LSB corresponds to the 18<sup>th</sup> bit.

For users, if STOP\_EN is configured to 0, stop bits are not sent. If it is configured to 1, stop bits with 1-8 symbols are sent.

## 2.7.9 Pause/Interval Configuration

| Register Name      | Bits | R/W | Bit Name             | Function Description                              |

|--------------------|------|-----|----------------------|---------------------------------------------------|

| CUS_PKT1<br>(0x08) | 6    | RW  | INTERVAL_EN          | Interval enabling bit.<br>0: disable              |

| (0,000)            |      |     |                      | 1: enable                                         |

|                    |      |     |                      | The Interval length can be configured to 0 ~ 255. |

| CUS PKT29          |      |     |                      | 0 represents sending 0 of 1 symbol, and so on,    |

| (0x24)             | 7:0  | RW  | INTERVAL_LENGTH<7:0> | 255 represents sending 0 of 256 symbols. The      |

| (0x24)             |      |     |                      | Symbol length is random.                          |

|                    |      |     |                      | Note that interval is fixed to sending 0.         |

#### Table 20. Pause/Interval Configuration Register

Notes

- In a strict sense, pause/interval is not an effective part of the packet structure, namely, it only sends a number of symbols of 0.

- For users, if INTERVAL\_EN is configured to 0, pause/interval is not sent. If it is configured to 1, a pause/interval with 1 ~ 256 symbols is sent.

## 2.7.10 Tcycle Configuration

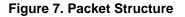

Tcycle refers to a transmission cycle (transmission process) in hardware packet Tx mode. A transmission cycle can contain several (N) repeated packet transmissions with the support of pause/interval between packets. It also supports transmitting m data groups in a transmission cycle with each data group composed of N packets. The different transmission cycle configurations are shown in the below figure.

- If Tcycle is disabled, the packet transmission follows the first method as shown in the above figure. If preamble is enabled, the preamble is fixed at the beginning of each packet.

- If both Tcycle and preamble are enabled and PREAMBLE\_LOCATION = 1, the packet transmission follows the second method as shown in the above figure. That is, a preamble appears once in a group locating at the beginning of each group and preamble appears M times (M = TXCYCLE) within one transmission cycle.

- If Both Tcycle and preamble are enabled, and PREAMBLE\_LOCATION = 0, the packet transmission follows the third method as shown in the above figure. That is, a preamble appears once in a group locating at the beginning of each group and preamble appears m\*n (TXCYCLE \* PKT\_NUM) within one transmission cycle.

#### Notes

- 1. In the above figure, P = Preamble, D = Sync/Head + Addr/ID + Key Value + LBD Status + Stop Bit.

- 2. If Preamble is disabled, preamble is not sent.

- 3. If Interval is disabled, interval is not sent.

- 4. If Tcycle is disabled, preamble\_location is configured to 0.

- 5. If Tcycle is disabled, Tcycle is configured to 0.

| Register Name | Bits | R/W | Bit Name          | Function Description                                   |

|---------------|------|-----|-------------------|--------------------------------------------------------|

|               | *    |     |                   | When Tcycle is enabled, it is the location of Preamble |

|               |      |     |                   | in the packet structure.                               |

|               | 2    | RW  | PREAMBLE_LOCATION | 0: In one cycle, each Packet contains 1 Preamble, i.e. |

| CUS_PKT1      | Z    | RVV |                   | in one cycle, N Packets contain N Preambles.           |

|               |      |     |                   | 1: In one cycle, only 1 Preamble is included, which is |

| (0x08)        |      |     |                   | only in the first Packet.                              |